MODELSIM DO FILE CODE

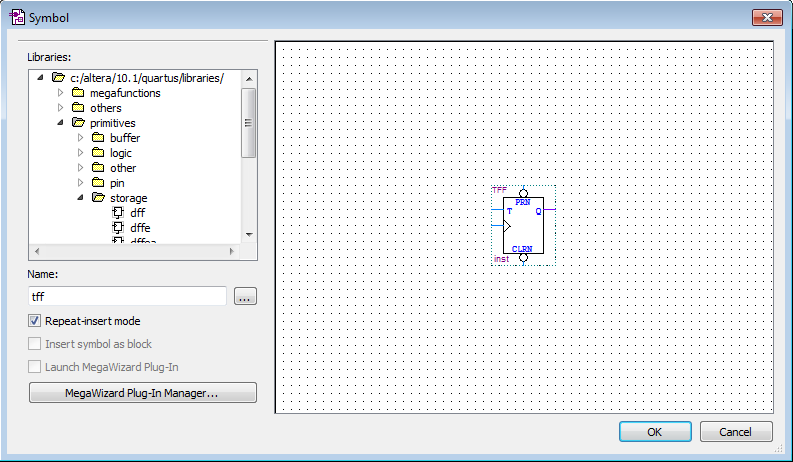

You have to be confident that your code is indeed interpreted as a ROM by altera, otherwise the attribute will be ignored. It is possible to find an IP Address using the Facebook messenger/chat application. A block diagram design of the FIR filter is shown in Figure 5. 2 filter input signal generated in MATLAB into Quartus II. As for using the quartus II tools, I just googled for stuff as it was needed.

MODELSIM DO FILE DOWNLOAD

Languages: English Download Canon PIXMA iP1800 Easy-PhotoPrint EX v. For ROMs, the memory is initialized with COE files. Modifications to cores generated by Coregen are not BRANDON BEN. The available IP cores depend on the target device. Under Other Options, provide a memory initization (COE) file and check "Load Init File".

MODELSIM DO FILE PDF

pdf (35 MB) Embedded IP Peripherals User Guide (used also in NIOS) - ug_embedded_ip_V11. Let Quartus infer an M9K from appropriate verilog (generally the best approach) 2. Whether the Quartus ROM IP core ROM introduction The data in the ROM needs to be initialized first.

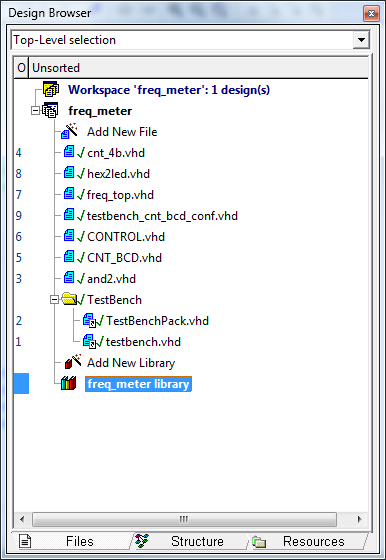

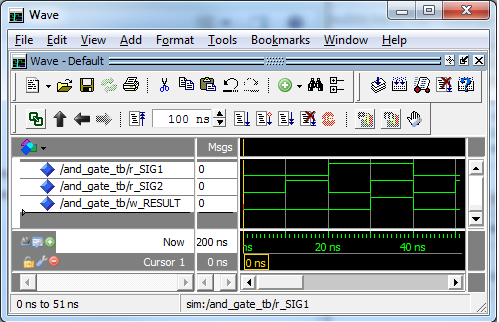

sROMet compiler - TSMC 40 nm uLPeFlash - Non volatile memory optimized for high density and low power - Dual Voltage - compiler range up to 1M. To finish the simulation session, choose End Simulation from the Simulation menu or type the endsim command in the Console window.Quartus rom ip 3) 5nm IP tape-out in Oct'21. The simulation results are presented in the figure above. Type in the run -all command in the Console window, which starts the simulation ( Simulation | Run). Select the top(only) unit and drag it to the waveform window. Open an empty waveform window by going to File | New | Waveform. Switch to the Structure tab of the Design Browser. Verify that all of the files compiled successfully, and that the correct top level is selected.įrom the Simulation menu, select the Initialize Simulation option. Select the top(only) entity/architecture pair in the Top-level Selection dialog box and click OK. See the on-line documentation for details.įrom the Design menu, select Compile All with File Reorder The list of files that have been processed during the import procedure is displayed in the Console window.Īn alternative to the procedure described above is the use of the importmodelsim command. It contains links to the HDL sources specified by the ModelSim project file. If you have started the import option and there was no Active-HDL design loaded, the new Active-HDL workspace is created and the new design (along with a library) is attached to the design tree displayed in the Design Browser window. If an Active-HDL workspace was loaded and you have started importing the ModelSim project, in the Open Design dialog box, choose whether the new Active-HDL design will be added to the current workspace or a new one. Before you choose the Save option, you may want to create a new working project subfolder for a new Active-HDL workspace/design.Ĭlick the Save button. In the Save In dialog box, specify the name and location for the Active-HDL design file (*.adf). For additional information, see Customizing Design Folders.Īfter you have selected the project file, click the Open button. NOTE: The default location of the files imported to the design can be changed in the Design Structure category of the Preferences dialog box.

0 kommentar(er)

0 kommentar(er)